連載

西川善司の3DGE:Ryzen 7000を支えるZen 4アーキテクチャのすべて。CPUコアに加えられた細かい改良とI/Oダイの見どころをひもとく

|

なお,Ryzen 7000のラインナップや,主なスペック,基本的な設計方針といった概略は,8月30日掲載のニュースで紹介済みなので,概要を知りたい,あるいはRyzen 7000の基礎情報を知らないという人は,そちらを最初に参照してほしい。

Zen 4とはどういったCPUなのか

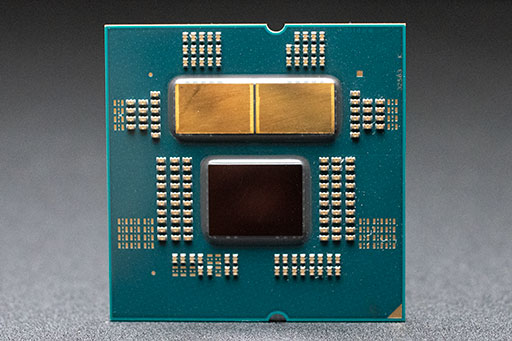

Ryzen 7000が採用するZen 4コアのCPUダイ(CPU Complex Die,以下 CCD)は,TSMCの5nm製造プロセスで製造されている。トランジスタ数は約65億個で,ダイサイズは70mm2であるという。ちなみに,Zen 3のCCDは7nm製造プロセスで製造され,総トランジスタ数とダイサイズはそれぞれ約42億個,約81mm2だったので,面積は約14%小さくなり,トランジスタ数は約55%も増えたということになる。ダイ面積が縮小したのにトランジスタ数が増えたのは,製造プロセスが7nmから5nmへ微細化したことの直接的な恩恵で間違いない。

|

Zen 2世代は,1クラスタあたり4 CPUコアで,それを2クラスタで構成していたが,Zen 3では,1クラスタあたり8 CPUコアの8-Core Complexに拡大した。Zen 4のCPUダイにおけるCPUコアの構成も,Zen 3と同じだ。Ryzen 7000においても,Ryzen 9系はCPUパッケージに2基のCPUダイを実装しており,Ryzen 7以下はCPUダイが1基となる。

Zen 2世代でRyzenは,CPUダイとI/Oダイを分離するアーキテクチャを採用したが,この点はZen 4でも変わっていない。I/Oダイについての詳細は後述するが,Zen 4における最大のトピックは,このI/OダイにGPUコアを内蔵できる点にある。

|

さて,Ryzen 7000の第一報掲載後,最も話題になったのはTDP(Thermal Design Power,

発表日に米国で行われたZen 4の技術説明会で,AMDは「たしかにTDPは上がった」と認めつつ,それ以上のメリットがあると説明する。

まず,5nmプロセスを採用したことで,Ryzen 5000よりも低電圧で駆動できるようになり,電力あたり性能が向上した。

|

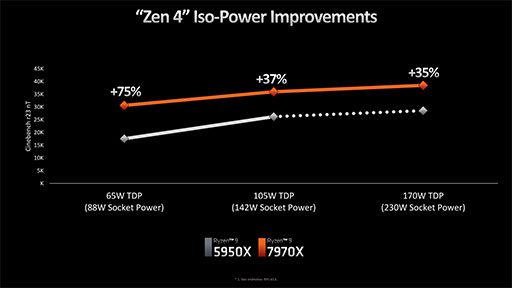

微細化の恩恵は,これだけに留まらない。Ryzen 7000は,Ryzen 5000と同等の電圧で駆動すると,先代よりも高い動作クロックで動作できるようになった。AMDによれば,同クラスのRyzen 5000を同等の消費電力で動作させた場合と比べて,Ryzen 7000は49%増,すなわち約1.5倍の性能を発揮するという。

しかし,消費電力や発熱量,TDPは,クロックに準じて上昇するので,高性能を追求して動作クロックを上げると,当然ながらTDPは上がってしまう。実際,Ryzen 7000の最上位モデルであるRyzen 9 7950XのTDPは170Wで,前世代最上位モデルのRyzen 9 5950Xが105Wだったのに比べれば,大幅に増えた。

結局のところ「デスクトップPC向けプロセッサの場合は,TDPが向上して高い性能が出せるのならば,そのほうが多くのユーザーは喜ぶだろうから,TDPを上げました」という,ことなのだろう。

|

|

Zen 4マイクロアーキテクチャの進化点を整理する

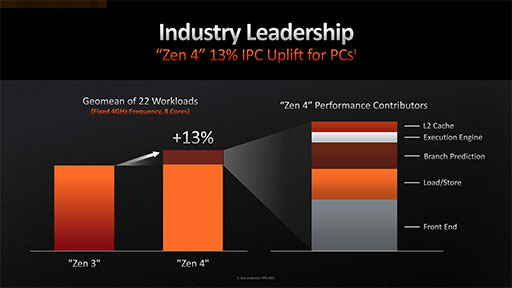

改めて言うことではないのかもしれないが,結論から言えば,Zen 4はZen 3をベースにした改良版である。これを踏まえたうえで,Zen 4のフロントエンドを見ていこう。

|

|

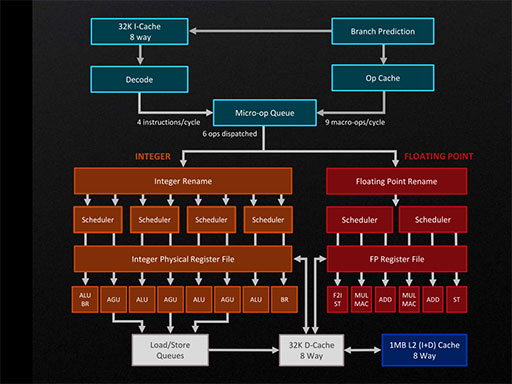

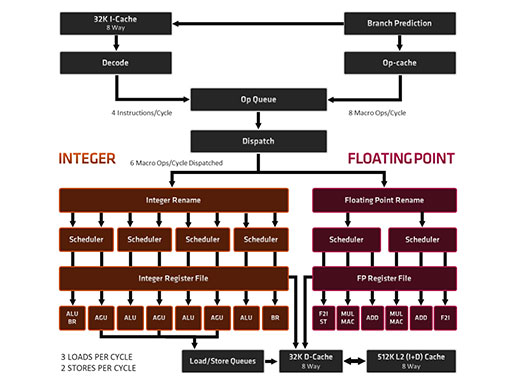

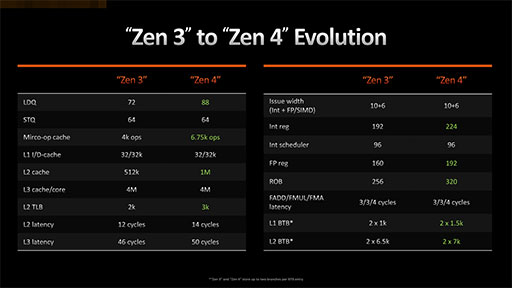

L1キャッシュは,命令キャッシュ(I-Cache)とデータキャッシュ(D-Cache)のどちらも,容量32KBであることは変更なし。ただ,I-Cache側の「Branch Target Buffer」(分岐先バッファ,以下 BTB)が,1.5倍(1536エントリー)に増えている。

一般的なCPUにおいて,分岐予測のメカニズムには,「Branch Prediction Buffer」(分岐予測バッファ,以下 BPB)とBTBという2種類のバッファを活用する。BPBは,分岐命令の結果,分岐先へ飛ぶか否かの推測を保持するバッファで,BTBは,分岐命令アドレスのタグ情報と,分岐命令のジャンプ先アドレス(プログラムカウンタ,PC)を保持している。基本的には,BTBが大きいと分岐予測は当たりやすくなって,分岐予測の性能は向上する。

ところで,x86系CPUでは,パイプラインの実行効率やアウトオブオーダー(命令実行順変更)が行いやすいように,本来のx86命令コードをRISC調の最小単位命令(Micro-Ops)に分解して実行するのが定番だ。そしてMicro-Opsの一塊(Macro-Ops)をキャッシュするのが,ブロック図の「Op Cache」である。

AMDは,Zen 4でOp cacheを68%も増量しており,1クロックあたりのMacro-Ops出力数が,Zen 3の8個に対して9個へと増えた。たかがプラス1ではあるが,Zen 3比では1.125倍なので,AMDは,この改良も効果が大きいと見ているようだ。

AMDは,こうした一連の改良によって,「分岐命令が多いプログラム」(Branchy Code)の実行効率が相応に向上したと説明している。

逆に,Micro-Opsの命令発行数はZen 3と同じで,1クロックあたりの6個のまま据え置かれた。

|

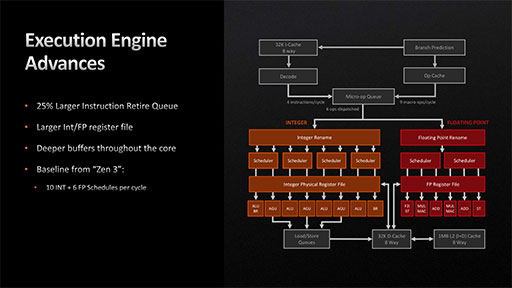

続いては,Zen 4の命令実行部を見てみよう。

|

アウトオブオーダーの処理を含めた命令実行のスケジューリングを行うのが,図中の「Scheduler」だ。アウトオブオーダーを行うときに演算結果を一時的に保存する「リオーダーバッファ」(AMDでは「Instruction Retire Queue」と称する)を,Zen 3の256命令分に対して,Zen 4では320命令分,すなわち25%増量しているのだ。

またAMDは,整数(Integer)演算や浮動小数点(Float)演算に用いるレジスタファイルも増量したと説明している。具体的には,整数レジスタが,Zen 3の192個からZen 4では224個へ17%,浮動小数点レジスタは160個から192個へと,20%も増えた。レジスタファイルの増大は,命令同時実行(スーパースカラ)の効率向上や,同時マルチスレッディング(Simultaneous Multi-Threading,SMT)の実行効率を向上させることにも効く。

演算の実働部隊である実行ユニットの数は,Zen 3と変わっていない。そのため,1クロックあたりの最大命令実行数は,整数演算命令が10個,浮動小数点演算命令は6個のままだ(10 INT+6 FP)。つまりZen 4では,Zen 3でもフル稼動できていなかった実行ユニットの実行効率を上げるために,フロントエンド部と分岐予測周り,レジスタファイルの増強を行ったということなのだろう。

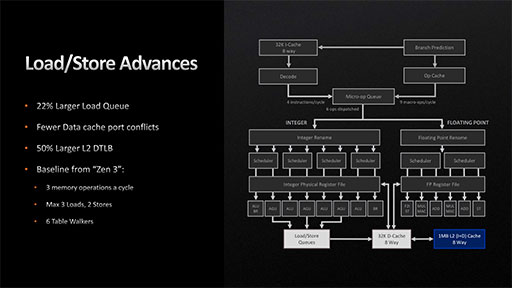

メモリアクセスを担当するロード/ストア処理系ブロックも,強化が行われた。

|

メモリ読み出しの依頼を一時的に溜め込み,最も低遅延な順番で実行していくためのキューイングを行う「Load Queue」は,Zen 3の72個から,Zen 4では88個,すなわち22%大きくなった。これにより,L1データキャッシュへの無駄なアクセスを減らしたそうだ。なお,メモリ書き出し用のStore Queueは,変化がないとのこと。

また,仮想アドレスから物理アドレスへの変換キャッシュする「Translation Lookaside Buffer」(TLB)は,「L2 Data TLB」(DTLB)がZen 3の2048エントリに対して,Zen 4では3072エントリと,50%も増えた。「これも,間接的にロード/ストア処理の低遅延化に貢献した」とAMDは説明する。

一方で,

- 1クロックあたり,3つのメモリアクセス実行

- 最大3つのメモリ読み出し(ロード)

- 最大2つのメモリ書き込み(ストア)

- DTLBへの同時参照(テーブルウォーク)数は6個

といったロード/ストア処理能力は,Zen 3と変わらない。

|

|

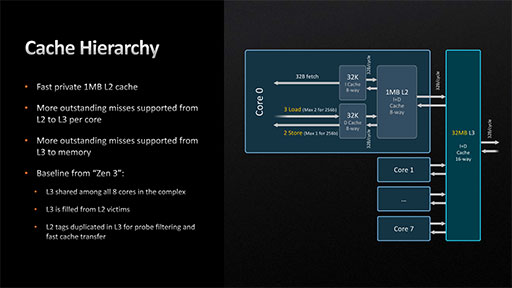

そのほかに,L2キャッシュは,Zen 3の1コアあたり容量512KBに対して,Zen 4では1MBへと倍増。シンプルにL2キャッシュのヒット率が上がることとなった。

次のスライドは,Zen 4のキャッシュ構造を示したものだが,キャッシュ周りの拡張ポイントはL2キャッシュの倍増くらいで,それ以外に大きな変更はない。たとえば,Zen 4のL3キャッシュ容量は,Zen 3から変更はなく,1クラスタあたり容量32MB(※2クラスタなら64MB)のままだ。AMDによると「Zen 4では,各コアのL2キャッシュ容量が増えたことで,Zen 3よりは相対的にL3キャッシュに対するキャッシュミスが減る」とのことなので,ここは据え置きでもよしということだろう。

|

こうして見ていくと,Zen 4とは,Zen 3に対して補助部分の強化を行った改良版というイメージがある。地道なチューニングを重ねて着実に性能を高めてきたZenマイクロアーキテクチャだが,はたしてマイクロアーキテクチャを刷新するのは,いつになるのだろうか。

幅広いAVX-512命令サポート

ただし演算は256bit単位

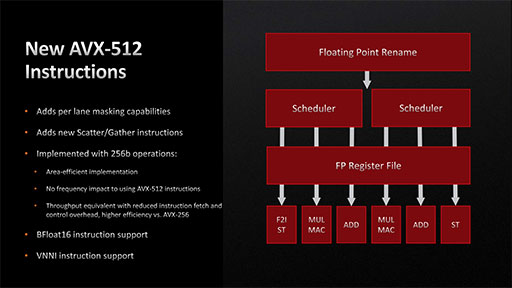

これまでのZenシリーズにはなく,Zen 4で新たに実装されたのが,「AVX-512」命令セットだ。

|

AVX-512は,512bit幅のレジスタやデータを用いるSIMD命令セットで,IntelのCPUでは,2017年登場の「Skylake-X」で採用となったものだ。ただ,今どきのIntel製CPUのすべてが対応しているわけではなく,最新の第12世代Coreプロセッサでは無効化されている。

Zen 4は,AVX-512命令セットの拡張命令(Extensions)も幅広くサポートしており,ニューラルネットワーク関連の演算や推論アクセラレーションに有用な「AVX-512 VNNI」命令セットや,精度よりもダイナミックレンジを重視するAI学習処理処理系に適した16bit浮動小数点「BF16」の演算命令「AVX-512 BF16」などをサポートする。

|

なおAMDは,AVX-512命令の実行に「Zen 3と同じく256bitの実行パイプ(256bitレジスタ含む)を,そのまま使用している」と説明していた。これはけっこう重要なポイントで,つまり,Zen 4のAVX-512命令は,512bit幅のデータを取り扱う命令セットではあるが,クロックあたりに処理できる(≒演算できる)のは256bitまでとなり,512bit分の演算は2回に分けて行うということである。

ただ,同時にAMDは,「AVX-512命令セットの実行は,同系の処理を2つのAVX-256命令セットで実装した場合よりは,圧倒的に速い」と述べていた。その理由は,「命令語のフェッチと処理系制御のオーバーヘッドを半分にできるから」とのこと。当たり前の説明ではある。

ちなみに,かつて初代ZenとZen+では,AVX-256命令セットに対応していたもののデータパスが128bit幅だったため,256bit幅のSIMD演算を2回に分けていたことがある。Zen 2では,データパスが256bit幅へ拡張されたので,1回で演算できるようになった。256bit幅のままAVX-512に対応したZen 4は,過去の対応を思い起こさせる。汎用ソフトウェアでAVX-512の活用が進めば,Zen 5以降において,データパス拡幅が行われ,ネイティブ512bit化が成されることがあるかもしれない。

I/OダイにRDNA 2世代のGPUコアを統合。ただし性能は期待できず

Zen 2以降,AMDは,メモリインタフェースやPCI Express(以下,PCIe)などの周辺I/O回路を「I/Oダイ」に集約して,CPUコアとは別チップ化する構成を採用している。この構成は,Zen 4でも受け継がれた。

I/Oダイを別チップにするのは,製造コストを抑えることと,CPUダイよりも高電圧で駆動することを考慮して,CPUダイよりは少し枯れた製造プロセスを採用するためだ。たとえば,Zen 2やZen 3はCPUダイに7nmプロセスを採用していたが,I/Oダイは14nmや12nmプロセスを用いていた。

かたやZen 4用のI/Oダイは,TSMCの6nmプロセスで製造しており,総トランジスタ数は約34億個,ダイサイズは122mm2であるという。最新プロセスではないにせよ,6nmプロセス採用やチップの規模は,今どきのCPUに引けを取らない。

こうなった理由は,複数ある。最も分かりやすい理由は,RyzenシリーズをノートPCに展開するときの最適化にある。PCの動作において稼働率の高いI/Oダイの消費電力を落とせれば,電力あたり性能で有利になる。優れた電力あたり性能は,ノートPCへの採用には欠かせない要素だ。その実現には,I/Oダイの微細化が最も手っ取り早いアプローチとなる。

さらに,微細化によってI/Oダイの面積に余裕が出たこともあり,Zen 4のI/Oダイは,GPUも内蔵することとなった。GPU名としては,「AMD Radeon Graphics」となっている。

|

I/OダイにGPUを内蔵すると聞いて,「APU系のRyzenはどうなるの?」と疑問を持つ人もいるだろう。回答としては「AMDは,今後もAPU製品を投入していく」とのことであった。というのも,このI/Oダイに組み込まれるGPUは,非常に限られた性能しかもたないのだ。

Ryzen 7000の内蔵GPUは,Radeon RX 6000シリーズと同じ「RDNA 2」世代のGPUではあるが,シェーダプロセッサ(SP)クラスタである「Compute Unit」(CU)はわずか2基だけだ。今どきのAMD製APUは,GPUの動作クロックが2GHz程度なので,これを当てはめて理論性能値を計算すると,

- 2 CU×64 SP×2 FLOPS×2GHz=0.5 TFLOPS

となる。9年前に登場したRadeon HD 7000系のエントリーモデル「Radeon HD 7730」が0.6 TFLOPS程度なので,とても今どきのゲームを快適にプレイできる性能ではない。しかし,Windowsの画面を表示して一般的なアプリを活用するだけであれば,必要な性能を持つのも確かだ。

なお,AMDに確認したところ「I/Oダイの内蔵GPUでは,Infinity Cacheを省略している」とのこと。RDNA 2世代GPUは,グラフィックス性能面でInfinity Cacheにかなり依存しているので,これを持たないGPUでのゲームプレイは,まったく期待しないほうがいい。

また,GPUコア部分には,ちゃんとレイトレーシングユニットを内蔵しているそうである。ただ,AMDのCTO(最高技術責任者)であるJoe Macri氏は「(レイトレーシングユニットを)使えることは使えるが,使うことはお勧めしない」と笑っていた。

さて,Zen 4のI/Oダイ内蔵GPUは,PCに単体GPUを接続している場合も有効化して,同時に使用できるとのこと。

たとえば,Radeon RX 6000シリーズのエントリー市場向けである「Radeon RX 6500」や「Radeon RX 6400」はコスト削減のために,ビデオエンコーダを省略しているが,これらをZen 4搭載PCに組み合わせて,ビデオエンコード処理をZen 4のI/Oダイ内蔵GPUに任せることはできるという(※アプリ側がGPUの選択に対応している必要があり)。

ちなみに,I/Oダイ内蔵GPUのビデオエンコーダは,H.265(HEVC)やH.264のエンコードに対応しており,H.265についてはHDR映像のエンコードとデコードも可能だ。ただ,AV1はデコードのみとなっている。

|

I/O機能については,PCIe 5.0対応などが大きなトピックである。

|

PCIe 5.0のレーン数が28というのも,地味ながら注目のポイントである。Zen 3のI/Oダイでは,PCIe 4.0が24レーンだったので,Zen 4のI/Oダイは4レーン増えたわけだ。PCIeレーン数が20のIntelプラットフォームに対する優位点と言えよう。

一方で,残念な点もある。Zen 4のI/Oダイは,「USB4」に対応していないのだ。AMDに質問したところ,「一般的なデスクトップPCユーザーは,USB4をそれほど重視していないと判断したため搭載しなかった。すでにノートPC向けRyzen 6000シリーズではUSB4に対応済みであることから分かるように,USB4に対応する技術がないわけではない」とのことだった。

ちなみに,「Zen 4のI/Oダイは,多めのPCIe 5.0のレーンを実装しているので,これらを活用してマザーボードメーカーがUSB4を独自に実装するマザーボードをリリースする可能性は高い。どうしても必要な時はそうしたマザーボードを選んでほしい」とのことだ。

ちなみに,Zen 4のI/Oダイは,20Gbps伝送とDisplayPort Alternate Modeに対応したUSB 3.2 Gen 2×2 Type-Cポートの配線を1系統備えている。AMDとしては,「デスクトップPC向けは,今のところこれで十分だ」と考えているようだ。

AM5対応チップセットの無印と“E”付きは何が違うのか

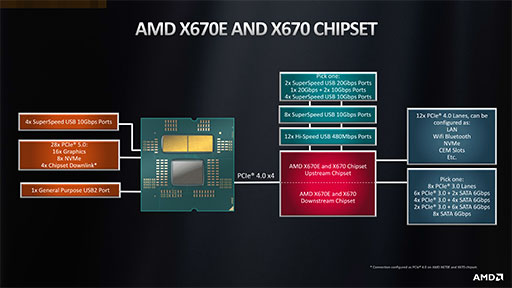

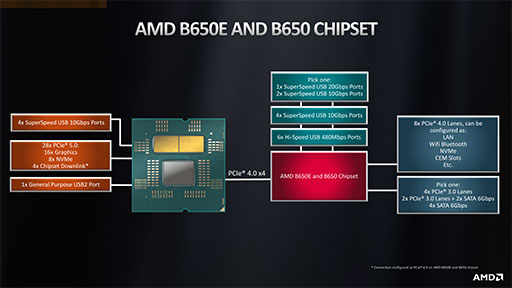

最後に,Zen 4世代に合わせて刷新されるAM5プラットフォーム対応チップセットについても触れておこう。

|

Socket AM5は,LGAタイプとなり,マイクロPGAタイプのSocket AM4とはソケット形状やピン形状,ピン数が異なる。ただ,HSF(Heatsink+Fan),すなわち冷却システムは,AM4のものを流用できるように配慮されている。

|

|

AM5プラットフォームの開始にあたって,AMDは,X670シリーズとB650シリーズシリーズという2種類のチップセットを提供する。これらのチップセットは,それぞれに“E”型番付きの上位版と,無印の下位版をラインナップしている。

次のスライドは,X670シリーズ,B650シリーズのそれぞれのチップセット備えるインタフェースを示したブロック図だ。なお,図中で左側にあるオレンジのインタフェース群は,Zen 4ベースCPUから直接引き出すものである。

|

|

|

なお,CPUから出る残りのPCIe 5.0 4レーン分は,チップセットとの接続用である。ただ,ブロック図からも分かるように,チップセットとの接続はPCIe 5.0ではなくPCIe 4.0だ。

本来であれば,CPUから出るPCIeインタフェースは,チップセットの種類によらず利用できるはずなのだが,製品ラインナップなどの都合で,PCIe 5.0 x16でGPUと接続できるのは“E”型番のX670Eチップセット,またはB650Eチップセット搭載マザーボードに限られる。無印版のX670/B650チップセットでは,GPUとの接続がPCIe 4.0 x16となってしまう点には注意しよう。

一方,CPUから出ているSSD接続用のPCIeレーンは,全チップセットでPCIe 5.0接続が可能となっている。ただ,一部のB650チップセット搭載マザーボードでは,SSD接続がPCIe 4.0に制限されるようだ。詳細な仕様は,マザーボードによって細かく変わるようなので,製品選びのときには,注意深く確認してほしい。

いずれにせよ,「PCIe 5.0を積極的に利用したい」という人は“E”型番のチップセットを搭載するマザーボードを選ぼう。

AMDのRyzenデスクトッププロセッサ製品情報ページ

- 関連タイトル:

Ryzen(Zen 4)

Ryzen(Zen 4) - この記事のURL: